- 您现在的位置:买卖IC网 > Sheet目录1997 > ICS601R-25ILF (IDT, Integrated Device Technology Inc)IC CLOCK MULTIPLIER 1:5 20-SSOP

DATASHEET

LOW PHASE NOISE 1 TO 5 CLOCK MULTIPLIER

ICS601-25

IDT / ICS LOW PHASE NOISE 1 TO 5 CLOCK MULTIPLIER

1

ICS601-25

REV E 051310

Description

The ICS601-25 is a low-cost, low phase noise, high

performance clock synthesizer for applications which

require low phase noise, low jitter, and low skew fanout. It is

IDT’s lowest phase noise multiplier, and also the lowest

CMOS part in the industry. Using IDT’s patented analong

and digital Phase Locked Loop (PLL) techniques, the chip

accepts a 10-27 MHz crystal or clock input, and produces

output clocks up to 156 MHz.

Features

Packaged in 20-pin SSOP

Uses fundamental 10 - 27 MHz crystal or clock

Output clocks up to 156 MHz

Low phase noise: -132 dBc/Hz at 10 kHz

Five low skew (<250 ps) outputs

Low jitter - 18 ps one sigma at 125 MHz

Full swing CMOS outputs with 25 mA drive capability at

TTL levels

Powerdown mode lowers power consumption

Advanced, low power, sub-micron CMOS process

Industrial temperature version available

Pb (lead) free package

Operating voltage of 3.3 V

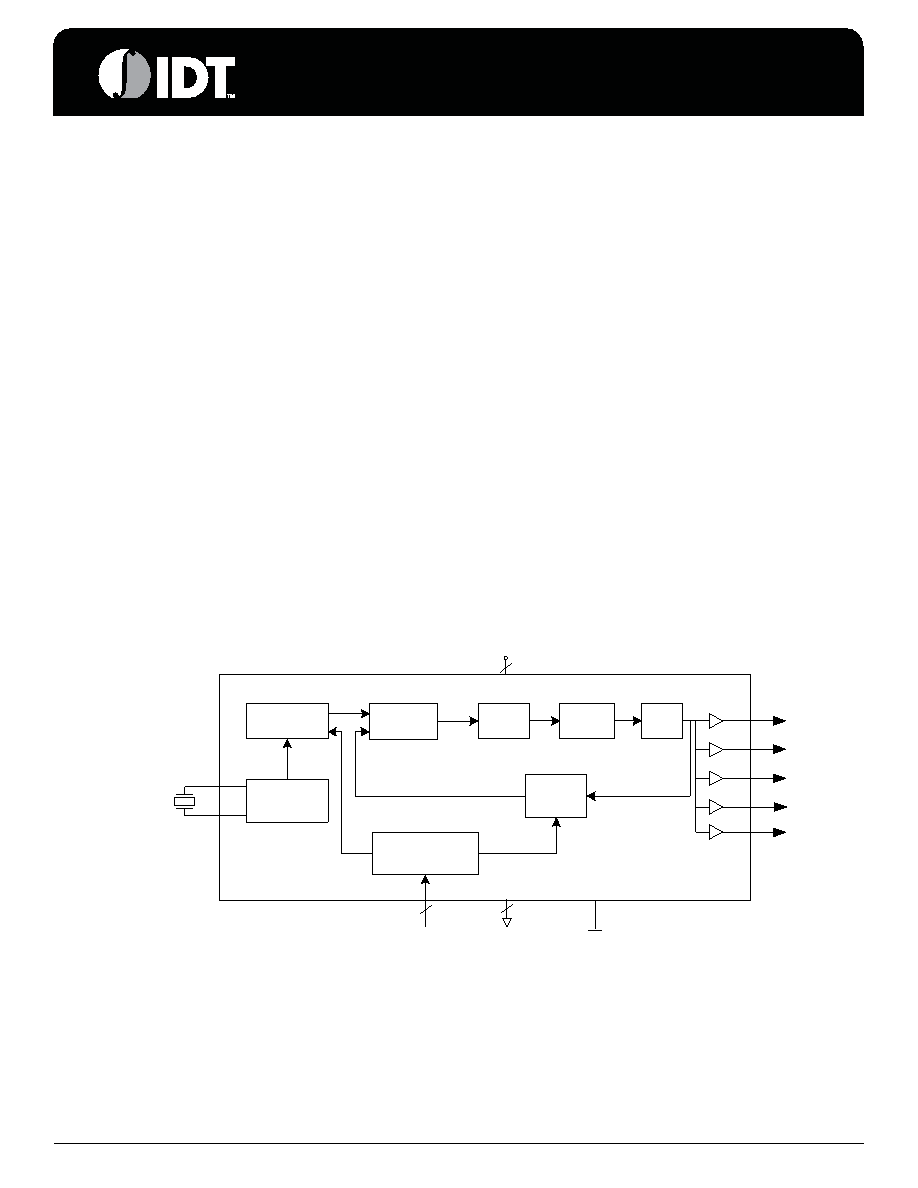

Block Diagram

CLK1

ROM Based

Multipliers

VCO

Divide

X1/ICLK

X2

Crystal or

clock input

Crystal

Oscillator

Reference

Divider

Phase

Comparator

VDD

Charge

Pump

Loop

Filter

VCO

S3:0

PD

CLK5

CLK4

CLK3

CLK2

5

GND

3

4

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS613MLF

IC CLOCK MULT LOW PHASE 16-SOIC

ICS650G-40ALFT

IC CLOCK ETHERNET SWITCH 16TSSOP

ICS650GI-44LF

IC CLK SYNTHESIZER 16-TSSOP

ICS650GI-47LF

IC CLK SYNTHESIZER 16-TSSOP

ICS650R-12LF

IC MPEG CLK SYNTHESIZER 20-SSOP

ICS650R-14LFT

IC NETWORKING SYSTEM CLK 20-SSOP

ICS650R-21ILF

IC CLK SOURCE SYSTEM PER 20-SSOP

ICS650R-22LF

IC CLK SOURCE PRV/STB 20-SSOP

相关代理商/技术参数

ICS601R-25ILFT

功能描述:IC CLOCK MULTIPLIER 1:5 20-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT

ICS601R-25IT

功能描述:IC CLOCK MULTIPLIER 1:5 20-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

ICS601R-25LF

功能描述:IC CLOCK MULTIPLIER 1:5 20-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND

ICS601R-25LFT

功能描述:IC CLOCK MULTIPLIER 1:5 20-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT

ICS601R-25T

功能描述:IC CLOCK MULTIPLIER 1:5 20-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

ICS604

制造商:ICS 制造商全称:ICS 功能描述:Intel Graphics Clock Source

ICS604M

制造商:ICS 制造商全称:ICS 功能描述:Intel Graphics Clock Source

ICS604MT

制造商:ICS 制造商全称:ICS 功能描述:Intel Graphics Clock Source